#### Features

- 32-bit ARM® Cortex -M3 processor

- 2.4 GHz IEEE 802.15.4-2003 transceiver & lower MAC

- 128 or 192 kB flash, with optional read protection

- 12 kB RAM memory

- AES128 encryption accelerator

- Flexible ADC, UART/SPI/TWI serial communications, and general purpose timers

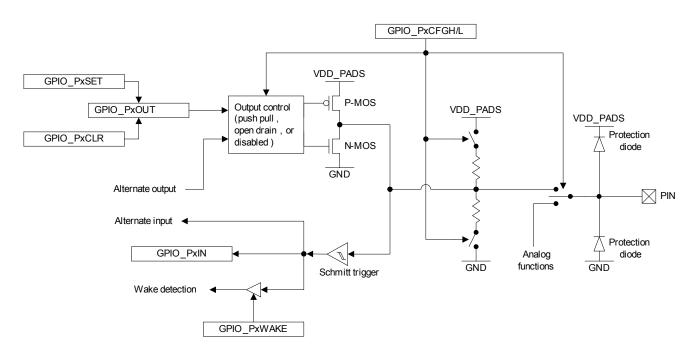

- 24 highly configurable GPIOs with Schmitt trigger inputs

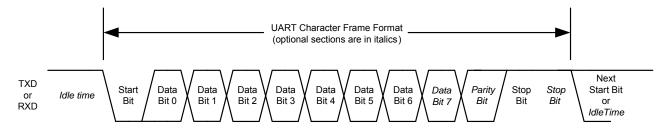

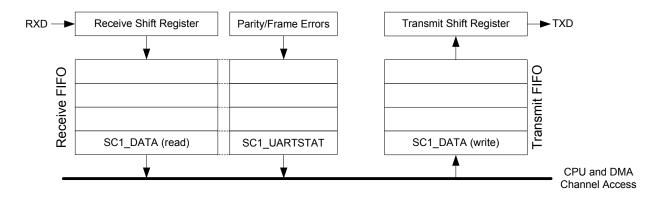

#### Industry-leading ARM® Cortex -M3 processor

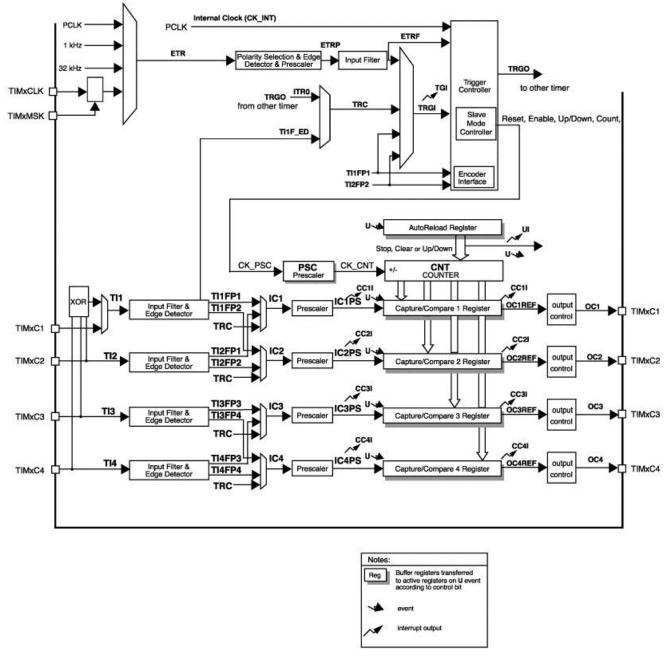

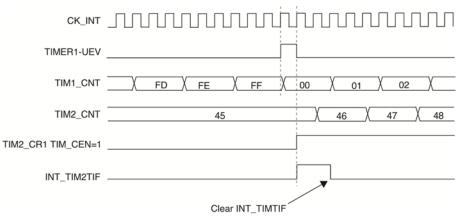

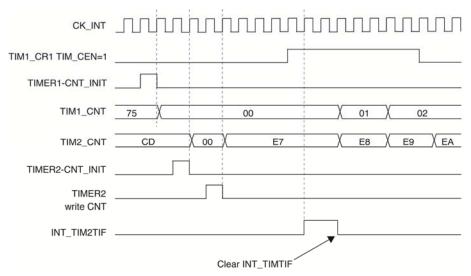

- Leading 32-bit processing performance

- Highly efficient Thumb-2 instruction set

- Operation at 6, 12, or 24 MHz

- Flexible Nested Vectored Interrupt Controller

#### Low power consumption, advanced management

- RX Current (w/ CPU): 26 mA

- TX Current (w/ CPU, +3 dBm TX): 31 mA

- Low deep sleep current, with retained RAM and GPIO: 400 nA without/800 nA with sleep timer

- Low-frequency internal RC oscillator for low-power sleep timing

- High-frequency internal RC oscillator for fast (110 µs) processor start-up from sleep

#### **Exceptional RF Performance**

- Normal mode link budget up to 103 dB; configurable up to 110 dB

- 100 dBm normal RX sensitivity; configurable to –102 dBm (1% PER, 20 byte packet)

- +3 dB normal mode output power; configurable up to +8 dBm

- Robust Wi-Fi and Bluetooth coexistence

#### Innovative network and processor debug

- Packet Trace Port for non-intrusive packet trace with Ember development tools

- Serial Wire/JTAG interface

- Standard ARM debug capabilities: Flash Patch & Breakpoint; Data Watchpoint & Trace; Instrumentation Trace Macrocell

#### **Application Flexibility**

- Single voltage operation: 2.1–3.6 V with internal 1.8 and 1.25 V regulators

- Optional 32.768 kHz crystal for higher timer accuracy

- Low external component count with single 24 MHz crystal

- Support for external power amplifier

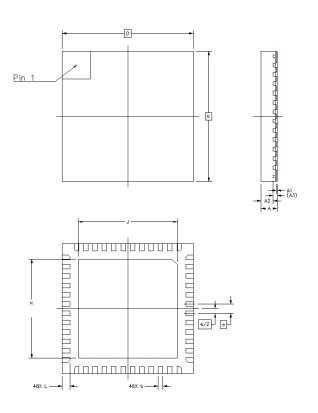

- Small 7x7 mm 48-pin QFN package

# **Table of Contents**

|    | Typical Application                              |     |

|----|--------------------------------------------------|-----|

| 2. | Electrical Specifications                        | 8   |

|    | 2.1. Absolute Maximum Ratings                    | 8   |

|    | 2.2. Recommended Operating Conditions            | 8   |

|    | 2.3. Environmental Characteristics               | 9   |

|    | 2.4. DC Electrical Characteristics               | 9   |

|    | 2.5. Digital I/O Specifications                  |     |

|    | 2.6. Non-RF System Electrical Characteristics    | .15 |

|    | 2.7. RF Electrical Characteristics               |     |

| 3. | Functional Description                           | .22 |

| 4. | Radio Module                                     | .25 |

|    | 4.1. Receive (RX) Path                           | .25 |

|    | 4.2. Transmit (TX) Path                          |     |

|    | 4.3. Calibration                                 |     |

|    | 4.4. Integrated MAC Module                       |     |

|    | 4.5. Packet Trace Interface (PTI)                |     |

|    | 4.6. Random Number Generator                     |     |

| 5. | ARM® Cortex <sup>™</sup> -M3 and Memory Modules  |     |

|    | 5.1. ARM® Cortex <sup>™</sup> -M3 Microprocessor |     |

|    | 5.2. Embedded Memory                             |     |

|    | 5.3. Memory Protection Unit                      |     |

| 6. | System Modules                                   |     |

|    | 6.1. Power Domains                               | .36 |

|    | 6.2. Resets                                      |     |

|    | 6.3. Clocks                                      |     |

|    | 6.4. System Timers                               |     |

|    | 6.5. Power Management                            | .46 |

|    | 6.6. Security Accelerator                        |     |

| 7. | GPIO (General Purpose Input/Output)              |     |

|    | 7.1. GPIO Ports                                  |     |

|    | 7.2. Configuration                               |     |

|    | 7.3. Forced Functions                            | -   |

|    | 7.4. Reset                                       |     |

|    | 7.5. Boot Configuration                          |     |

|    | 7.6. GPIO Modes                                  |     |

|    | 7.7. Wake Monitoring                             |     |

|    | 7.8. External Interrupts                         |     |

|    | 7.9. Debug Control and Status                    |     |

|    | 7.10.GPIO Signal Assignment Summary              |     |

|    | 7.11.Registers                                   |     |

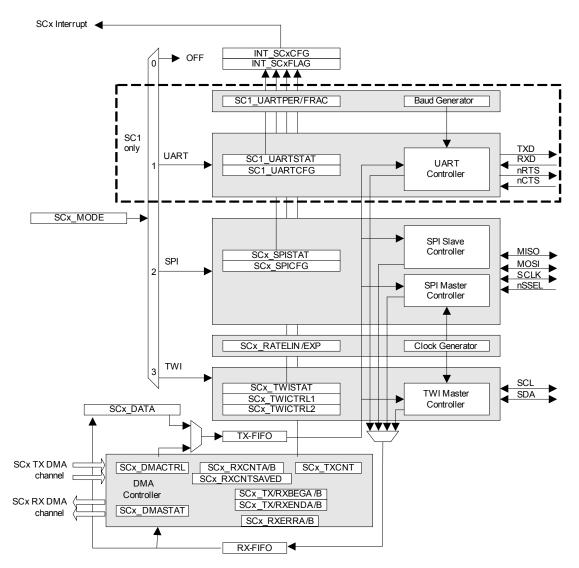

| 8. | Serial Controllers                               |     |

|    | 8.1. Overview                                    |     |

|    | 8.2. Configuration                               |     |

|    | 8.3. SPI - Master Mode                           | .76 |

| 8.4. SPI - Slave Mode              |                             |     |

|------------------------------------|-----------------------------|-----|

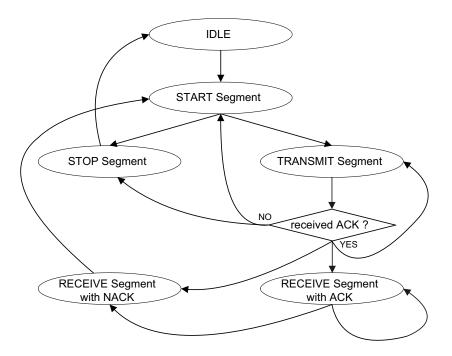

| 8.5. TWI - Two Wire serial Interfa | aces                        |     |

|                                    | nous Receiver / Transmitter |     |

| 8.7. DMA Channels                  |                             |     |

| 9. General Purpose Timers (TIM1    | and TIM2)                   |     |

| 9.1. Introduction                  | ,                           |     |

|                                    |                             |     |

| 0                                  | n                           |     |

| •                                  |                             |     |

|                                    |                             |     |

|                                    | rter)                       |     |

|                                    | ,                           |     |

|                                    |                             |     |

| •                                  |                             |     |

| •                                  |                             |     |

| 10.5.ADC Key Parameters            |                             |     |

| -                                  |                             |     |

| 0                                  |                             |     |

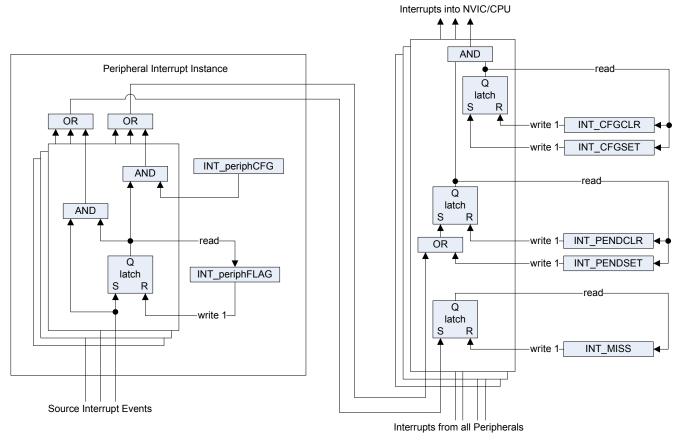

|                                    | Controller (NVIC)           |     |

| •                                  |                             |     |

|                                    | MI)                         |     |

|                                    | ,                           |     |

| 11.5.Registers                     |                             |     |

| •                                  | J)                          |     |

|                                    | éll (ITM)                   |     |

|                                    | WT)                         |     |

|                                    | РВ)                         |     |

|                                    | ,                           |     |

|                                    | iterface                    |     |

|                                    |                             |     |

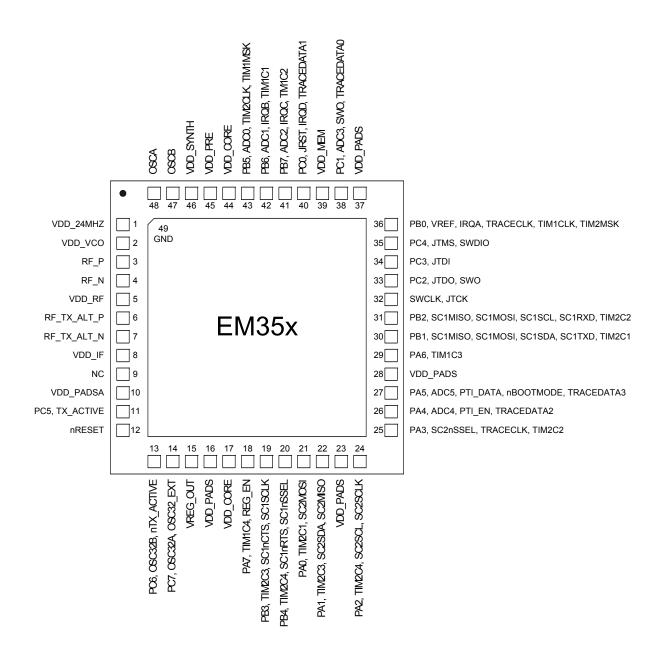

| 19. Pin Definitions                |                             | 211 |

| 19.1.Pin Definitions               |                             | 211 |

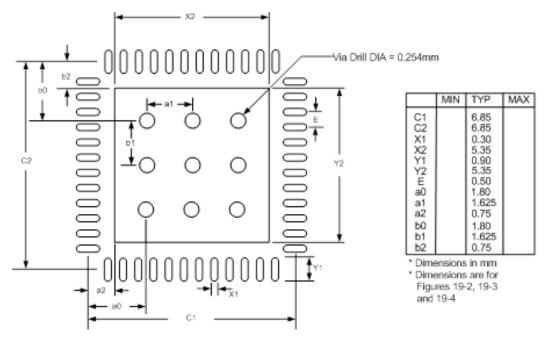

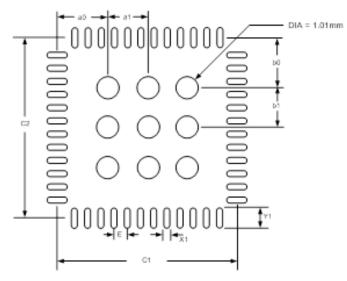

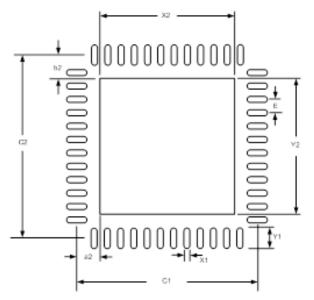

| 20. Package                        |                             |     |

| 20.1.QFN48 Footprint Recomme       | endations                   |     |

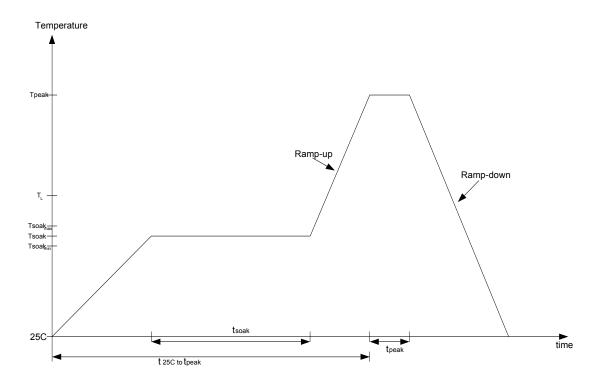

| 20.2.Solder Temperature Profile    |                             |     |

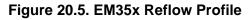

| 21. Top Marking                    |                             | 227 |

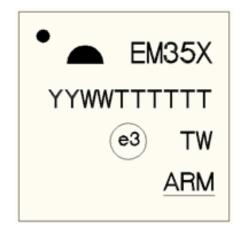

| 22. Shipping Box Label             |                             |     |

|                                    | able                        |     |

| Appendix B—Abbreviations and A     | Acronyms                    | 235 |

| Appendix C—References              | -                           | 239 |

| Document Change List               |                             | 240 |

| Contact Information                |                             | 241 |

# 1. Typical Application

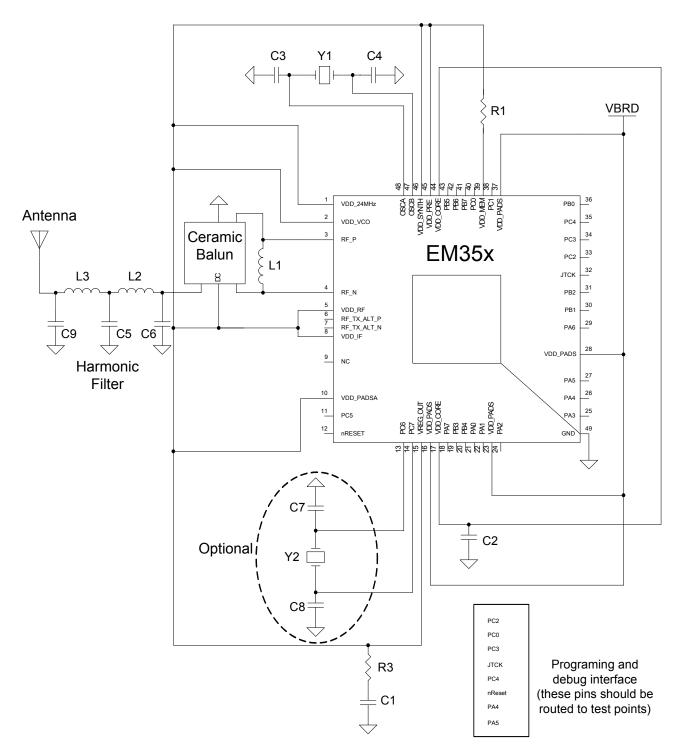

Figure 1.1 illustrates the typical application circuit, and Table 1.1 contains an example bill of materials (BOM) for the off-chip components required by the EM35x.

**Note:** The circuit shown in Figure 1.1 is for example purposes only, and the BOM is for budgetary quotes only. For a complete reference design, please download one of the latest Ember Hardware Reference Designs from the Silicon Labs website (www.silabs.com/zigbee-support).

The Balun provides an impedance transformation from the antenna to the EM35x for both TX and RX modes.

L1 tunes the impedance presented to the RF port for maximum transmit power and receive sensitivity.

The harmonic filter (L2, L3, C5, C6 and C9) provides additional suppression of the second harmonic, which increases the margin over the FCC limit.

The 24 MHz crystal Y1 with loading capacitors is required and provides the high-frequency crystal oscillator source for the EM35x's main system clock. The 32.768 kHz crystal with loading capacitors generates a highly accurate low-frequency crystal oscillator for use with peripherals, but it is not mandatory as the low-frequency internal RC oscillator can be used.

Loading capacitance and ESR (C1 and R3) provides stability for the internal 1.8 V regulator.

Loading capacitance C2 provides stability for the internal 1.25 V regulator, no ESR is required because it is contained within the chip.

Resistor R1 reduces the operating voltage of the flash memory, this reduces current consumption and improves sensitivity by 1 dB when compared to not using it.

Various decoupling capacitors are required, these should be placed as close to their corresponding pins as possible. For values and locations see one of the latest reference designs.

An antenna matched to 50  $\Omega$  is required.

Figure 1.1. Typical Application Circuit

Table 1.1 contains a typical Bill of Materials for the application circuit shown in Figure 1.1. The information within this table should be used for a rough cost analysis. For a more detailed BOM, please refer to one of Ember EM35x-based reference designs at the Silicon Labs website (www.silabs.com/zigbee-support).

| Item | Qty | Reference     | Description                                                           | Manufacturer                                                        |

|------|-----|---------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|

| 1    | 1   | C2            | CAPACITOR, 1 µF, 6.3 V, X5R, 10%, 0402                                | <not specified=""></not>                                            |

| 2    | 1   | C1            | CAPACITOR, 2.2 µF, 10 V, X5R, 10%, 0603                               | <not specified=""></not>                                            |

| 3    | 1   | C7            | CAPACITOR, 22 pF, ±5%, 50 V, NPO, 0402                                | <not specified=""></not>                                            |

| 4    | 2   | C3,C4         | CAPACITOR, 18 pF, ±5%, 50 V, NPO, 0402                                | <not specified=""></not>                                            |

| 5    | 1   | C8            | CAPACITOR, 33 pF, ±5%, 50 V, NPO, 0402                                | <not specified=""></not>                                            |

| 6    | 2   | C5, C9        | CAPACITOR, 1 pF, ±0.25 pF, 50 V, 0402, NPO                            | <not specified=""></not>                                            |

| 7    | 1   | C6            | CAPACITOR, 1.8 pF, ±0.25 pF, 50 V, 0402, NPO                          |                                                                     |

| 8    | 1   | L1            | INDUCTOR, 5.1 nH, ±0.3 nH, 0402 MULTILAYER                            | Murata LQG15HS5N1                                                   |

| 9    | 2   | L2, L3        | INDUCTOR, 2.7 nH, ±0.3 nH, 0402, MULTILAYER                           | Murata LQG15HS2N7                                                   |

| 10   | 1   | R1            | RESISTOR, 10 Ω, 5%, 0402                                              | <not specified=""></not>                                            |

| 11   | 1   | R3            | RESISTOR, 1 Ω, 5%, 0402                                               | <not specified=""></not>                                            |

| 12   | 1   | U1            | EM35x SINGLE-CHIP ZIGBEE/802.15.4-2003<br>SOLUTION                    | Ember EM35x                                                         |

| 13   | 1   | Y1            | CRYSTAL, 24.000 MHz, ±25 ppm STABILITY<br>OVER –40 to +85 °C, 18 pF   | ILSI, Abracon, KDS,<br>Epson                                        |

| 14   | 1   | Y2 (Optional) | CRYSTAL, 32.768 kHz, ±20 ppm INITIAL TOLER-<br>ANCE AT +25°C, 12.5 pF | Abracon, KDS, Epson                                                 |

| 15   | 1   | BLN1          | BALUN, CERAMIC 50/200 Ω                                               | Wurth 748421245<br>Johanson<br>2450BL15B100E<br>Murata LDB212G4010C |

| 16   | 1   | ANT1          | ANTENNA                                                               | Johanson<br>2450AT18B100E                                           |

Table 1.1. Bill of Materials for Typical Application Circuit

# 2. Electrical Specifications

## 2.1. Absolute Maximum Ratings

Table 2.1 lists the absolute maximum ratings for the EM35x.

## Table 2.1. Absolute Maximum Ratings

| Parameter                                                                                                                    | Test Condition                     | Min         | Max                | Unit |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------|--------------------|------|

| Regulator input voltage (VDD_PADS)                                                                                           |                                    | -0.3        | +3.6               | V    |

| Analog, Memory and Core voltage (VDD_24MHZ,<br>VDD_VCO, VDD_RF, VDD_IF, VDD_PADSA,<br>VDD_MEM, VDD_PRE, VDD_SYNTH, VDD_CORE) |                                    | -0.3        | +2.0               | V    |

| Voltage on RF_P,N; RF_TX_ALT_P,N                                                                                             |                                    | -0.3        | +3.6               | V    |

| RF Input Power<br>(for max level for correct packet reception see<br>Table 2.7)                                              | RX signal into a lossless<br>balun |             | +15                | dBm  |

| Voltage on any GPIO (PA[7:0], PB[7:0], PC[7:0]),<br>SWCLK, nRESET, VREG_OUT                                                  |                                    | -0.3        | VDD_PAD<br>S +0.3  | V    |

| Voltage on any GPIO pin (PA4, PA5, PB5, PB6, PB7, PC1), when used as an input to the general purpose ADC                     |                                    | -0.3        | 2.0                | V    |

| Voltage on OSCA, OSCB, NC                                                                                                    |                                    | -0.3        | VDD_PAD<br>SA +0.3 | V    |

| Storage temperature                                                                                                          |                                    | -40         | +140               | °C   |

| Note: Exposure to absolute-maximum-rated conditions for e                                                                    | xtended periods may affect device  | e reliabili | ty.                |      |

## 2.2. Recommended Operating Conditions

Table 2.2 lists the rated operating conditions of the EM35x.

## **Table 2.2. Operating Conditions**

| Parameter                                                                                                             | Test Condition                     | Min        | Тур         | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|------------|-------------|------|------|

| Regulator input voltage (VDD_PADS)                                                                                    |                                    | 2.1        |             | 3.6  | V    |

| Analog and memory input voltage<br>(VDD_24MHZ, VDD_VCO, VDD_RF, VDD_IF,<br>VDD_PADSA, VDD_MEM, VDD_PRE,<br>VDD_SYNTH) |                                    | 1.7        | 1.8         | 1.9  | V    |

| Core input voltage when supplied from internal regulator (VDD_CORE)                                                   |                                    | 1.18       | 1.25        | 1.32 | V    |

| Core input voltage when supplied externally (VDD_CORE)                                                                |                                    | 1.18       | _           | 1.9  | V    |

| Operating temperature range, T <sub>A</sub>                                                                           |                                    | -40        | _           | +85  | °C   |

| Note: Exposure to absolute-maximum-rated condition                                                                    | ons for extended periods may affec | t device r | eliability. |      |      |

## 2.3. Environmental Characteristics

Table 2.3 lists the rated environmental characteristics of the EM35x.

## **Table 2.3. Environmental Characteristics**

| Parameter                                                                                   | Symbol        | Test Condition | Min | Тур  | Max  | Unit |  |

|---------------------------------------------------------------------------------------------|---------------|----------------|-----|------|------|------|--|

| ESD (human body model)                                                                      |               | On any pin     |     | —    | ±2   | kV   |  |

| ESD (charged device model)                                                                  |               | Non-RF pins    | _   | _    | ±400 | V    |  |

| ESD (charged device model)                                                                  |               | RF pins        | _   | _    | ±225 | V    |  |

| Package Thermal Resistance*                                                                 | $\theta_{JA}$ |                |     | 27.1 |      | °C/W |  |

| *Note: Thermal resistance assumes multi-layer PCB with exposed pad soldered to a PCB board. |               |                |     |      |      |      |  |

## 2.4. DC Electrical Characteristics

Table 2.4 lists the dc electrical characteristics of the EM35x.

#### Table 2.4. DC Characteristics

Measured on Silicon Labs' EM357 reference design with T<sub>A</sub> = 25 °C and V<sub>DD</sub> = 3 V, unless otherwise noted.

| Parameter                                           | Test Condition                     | Min  | Тур  | Мах  | Unit |

|-----------------------------------------------------|------------------------------------|------|------|------|------|

| Regulator input voltage<br>(VDD_PADS)               |                                    | 2.1  | —    | 3.6  | V    |

| Power supply range (VDD_MEM)                        | Regulator output or external input | 1.7  | 1.8  | 1.9  | V    |

| Power supply range (VDD_CORE)                       | Regulator output                   | 1.18 | 1.25 | 1.32 | V    |

| Deep Sleep Current                                  |                                    |      |      |      |      |

| Quiescent current, internal RC                      | -40 °C, VDD_PADS=3.6 V             | _    | 0.4  |      | μA   |

| oscillator disabled                                 | +25 °C, VDD_PADS=3.6 V             |      | 0.4  |      | μA   |

|                                                     | +85 °C, VDD_PADS=3.6 V             |      | 0.7  |      | μA   |

| Quiescent current, including internal RC oscillator | -40 °C, VDD_PADS=3.6 V             | _    | 0.7  |      | μA   |

|                                                     | +25 °C, VDD_PADS=3.6 V             |      | 0.7  |      | μA   |

|                                                     | +85°C, VDD_PADS=3.6 V              |      | 1.1  |      | μA   |

| Quiescent current, including                        | -40 °C, VDD_PADS=3.6 V             | _    | 0.8  |      | μA   |

| 32.768 kHz oscillator                               | +25 °C, VDD_PADS=3.6 V             |      | 1.0  |      | μA   |

|                                                     | +85 °C, VDD_PADS=3.6 V             | —    | 1.5  | —    | μA   |

| Quiescent current, including                        | -40 °C, VDD_PADS=3.6 V             | _    | 1.1  |      | μA   |

| internal RC oscillator and<br>32,768 kHz oscillator | +25 °C, VDD_PADS=3.6 V             |      | 1.3  |      | μA   |

| SZ. 700 KHZ USCHIALOI                               | +85 °C, VDD_PADS=3.6 V             | —    | 1.8  | —    | μA   |

| Simulated deep sleep (debug mode) current           | With no debugger activity          | -    | 300  | —    | μΑ   |

Table 2.4. DC Characteristics (Continued)Measured on Silicon Labs' EM357 reference design with  $T_A = 25$  °C and  $V_{DD} = 3$  V, unless otherwise noted.

| Parameter                                                                      | Test Condition                                                                                                                                                                                      | Min | Тур  | Max | Unit |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Reset Current                                                                  | · · · · · ·                                                                                                                                                                                         |     |      |     |      |

| Quiescent current, nRESET asserted                                             | Typ at 25 °C/3.0 V<br>Max at 85 °C/3.6 V                                                                                                                                                            |     | 1.2  | 2.0 | mA   |

| Processor and Peripheral Curren                                                | its                                                                                                                                                                                                 |     |      |     |      |

| ARM <sup>®</sup> Cortex <sup>TM</sup> -M3, RAM, and flash memory               | 25 °C, 1.8 V memory and<br>1.25 V core<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 running at 12 MHz<br>from crystal oscillator<br>Radio and all peripherals off                                   |     | 6.5  | _   | mA   |

| ARM <sup>®</sup> Cortex <sup>TM</sup> -M3, RAM, and flash memory               | 25 °C, 1.8 V memory and<br>1.25 V core<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 running at 24 MHz<br>from crystal oscillator<br>Radio and all peripherals off                                   |     | 7.5  | _   | mA   |

| ARM <sup>®</sup> Cortex <sup>TM</sup> -M3, RAM, and flash memory sleep current | 25 °C, 1.8 V memory and<br>1.25 V core<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 sleeping, CPU<br>clock set to 12 MHz from the crystal<br>oscillator<br>Radio and all peripherals off            |     | 3.0  |     | mA   |

| ARM <sup>®</sup> Cortex <sup>TM</sup> -M3, RAM, and flash memory sleep current | 25 °C, 1.8 V memory and<br>1.25 V core<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 sleeping, CPU<br>clock set to 6 MHz from the high fre-<br>quency RC oscillator<br>Radio and all peripherals off |     | 2.0  | _   | mA   |

| Serial controller current                                                      | For each controller at maximum data rate                                                                                                                                                            | —   | 0.2  | _   | mA   |

| General purpose timer current                                                  | For each timer at maximum clock rate                                                                                                                                                                | _   | 0.25 |     | mA   |

| General purpose ADC current                                                    | At maximum sample rate, DMA enabled                                                                                                                                                                 | _   | 1.1  | _   | mA   |

| RX Current                                                                     |                                                                                                                                                                                                     |     |      |     |      |

| Radio receiver, MAC, and base-<br>band                                         | ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 sleeping, CPU<br>clock set to 12 MHz                                                                                                                      | _   | 22.0 | _   | mA   |

| Total RX current ( = $I_{Radio}$ receiver,<br>MAC and baseband, CPU + IRAM,    | 25 °C, VDD_PADS=3.0 V<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 running at 12 MHz                                                                                                                | _   | 25.5 | _   | mA   |

| and Flash memory)                                                              | 25 °C, VDD_PADS=3.0 V<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 running at 24 MHz                                                                                                                | _   | 26.5 | _   | mA   |

| Boost mode total RX current ( = I <sub>Radio</sub> receiver, MAC and base-     | 25 °C, VDD_PADS=3.0 V<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 running at 12 MHz                                                                                                                |     | 27.5 | —   | mA   |

| band, CPU+ IRAM, and flash memory )                                            | 25 °C, VDD_PADS=3.0 V<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 running at 24 MHz                                                                                                                |     | 28.5 | _   | mA   |

Table 2.4. DC Characteristics (Continued)Measured on Silicon Labs' EM357 reference design with  $T_A = 25$  °C and  $V_{DD} = 3$  V, unless otherwise noted.

| Parameter                                                                                                    | Test Condition                                                                                                                             | Min | Тур  | Max | Unit |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| TX Current                                                                                                   |                                                                                                                                            |     |      |     |      |

| Radio transmitter, MAC, and base-<br>band                                                                    | 25 °C and 1.8 V core; max. power out<br>(+3 dBm typical)<br>ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 sleeping, CPU<br>clock set to 12 MHz | _   | 26.0 | _   | mA   |

| Total TX current ( = I <sub>Radio</sub> transmit-<br>ter, MAC and baseband, CPU +<br>IRAM, and flash memory) | 25 °C, VDD_PADS=3.0 V; maximum<br>power setting (+8 dBm); ARM <sup>®</sup><br>Cortex <sup>TM</sup> -M3 running at 12 MHz                   |     | 42.5 |     | mA   |

|                                                                                                              | 25 °C, VDD_PADS=3.0 V; +3 dBm<br>power setting; ARM <sup>®</sup> Cortex <sup>TM</sup> -M3<br>running at 12 MHz                             | _   | 30.0 | _   | mA   |

|                                                                                                              | 25 °C, VDD_PADS=3.0 V; 0 dBm power<br>setting; ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 running at<br>12 MHz                              | _   | 27.5 | —   | mA   |

|                                                                                                              | 25 °C, VDD_PADS=3.0 V; minimum<br>power setting; ARM <sup>®</sup> Cortex <sup>TM</sup> -M3<br>running at 12 MHz                            | _   | 21.5 | _   | mA   |

|                                                                                                              | 25 °C, VDD_PADS=3.0 V; maximum<br>power setting (+8 dBm); ARM <sup>®</sup> Cor-<br>tex <sup>TM</sup> -M3 running at 24 MHz                 | —   | 43.5 | —   | mA   |

|                                                                                                              | 25 °C, VDD_PADS=3.0 V; +3 dBm<br>power setting; ARM <sup>®</sup> Cortex <sup>TM</sup> -M3<br>running at 24 MHz                             | _   | 31.0 | —   | mA   |

|                                                                                                              | 25 °C, VDD_PADS=3.0 V; 0 dBm power<br>setting; ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 running at<br>24 MHz                              | _   | 28.5 | _   | mA   |

|                                                                                                              | 25 °C, VDD_PADS=3.0 V; minimum<br>power setting; ARM <sup>®</sup> Cortex <sup>TM</sup> -M3<br>running at 24 MHz                            | _   | 22.5 | _   | mA   |

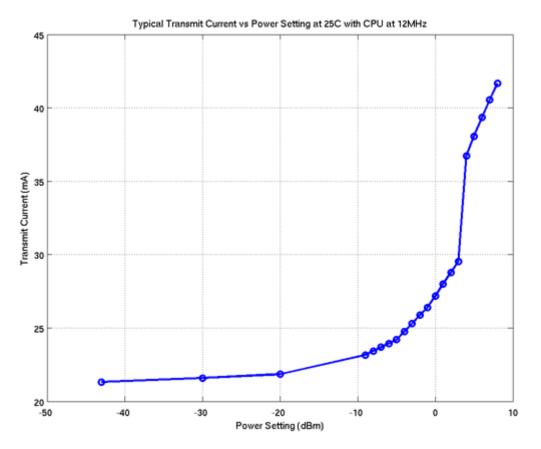

Figure 2.1 shows the variation of current in transmit mode (with the ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 running at 12 MHz).

Figure 2.1. Transmit Power Consumption

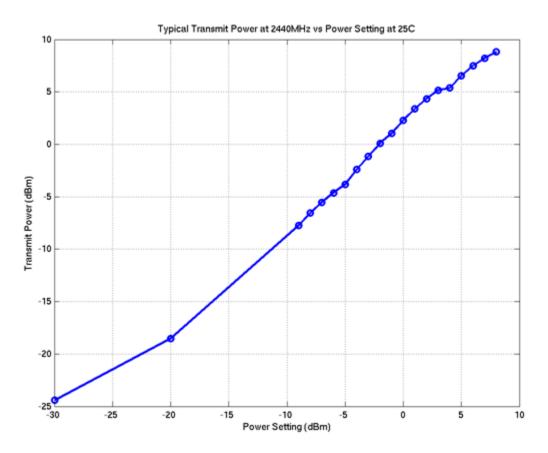

Figure 2.2. Transmit Output Power

# 2.5. Digital I/O Specifications

Table 2.5 lists the digital I/O specifications for the EM35x. The digital I/O power (named VDD\_PADS) comes from three dedicated pins (pins 23, 28 and 37). The voltage applied to these pins sets the I/O voltage.

## Table 2.5. Digital I/O Specifications

| Parameter                                                          | Test Condition                                                                               | Min                | Тур | Max                | Unit |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| Voltage supply (regulator input voltage)                           |                                                                                              | 2.1                | _   | 3.6                | V    |

| Low Schmitt switching threshold                                    | V <sub>SWIL</sub><br>Schmitt input threshold going<br>from high to low                       | 0.42 x<br>VDD_PADS | _   | 0.50 x<br>VDD_PADS | V    |

| High Schmitt switching threshold                                   | V <sub>SWIH</sub><br>Schmitt input threshold going<br>from low to high                       | 0.62 x<br>VDD_PADS | _   | 0.80 x<br>VDD_PADS | V    |

| Input current for logic 0                                          | Ι <sub>ΙL</sub>                                                                              | —                  | —   | -0.5               | μA   |

| Input current for logic 1                                          | I <sub>IH</sub>                                                                              | —                  | —   | +0.5               | μA   |

| Input pull-up resistor value                                       | R <sub>IPU</sub>                                                                             | 24                 | 29  | 34                 | kΩ   |

| Input pull-down resistor value                                     | R <sub>IPD</sub>                                                                             | 24                 | 29  | 34                 | kΩ   |

| Output voltage for logic 0                                         | V <sub>OL</sub><br>(I <sub>OL</sub> = 4 mA for standard pads,<br>8 mA for high current pads) | 0                  | —   | 0.18 x<br>VDD_PADS | V    |

| Output voltage for logic 1                                         | V <sub>OH</sub><br>(I <sub>OH</sub> = 4 mA for standard pads,<br>8 mA for high current pads) | 0.82 x<br>VDD_PADS | _   | VDD_PADS           | V    |

| Output source current<br>(standard current pad)                    | I <sub>OHS</sub>                                                                             | _                  | —   | 4                  | mA   |

| Output sink current<br>(standard current pad)                      | I <sub>OLS</sub>                                                                             | _                  | —   | 4                  | mA   |

| Output source current high current pad:<br>PA6, PA7, PB6, PB7, PC0 | І <sub>ОНН</sub>                                                                             | _                  | —   | 8                  | mA   |

| Output sink current high current pad:<br>PA6, PA7, PB6, PB7, PC0   | I <sub>OLH</sub>                                                                             | —                  | —   | 8                  | mA   |

| Total output current (for I/O Pads)                                | I <sub>OH</sub> + I <sub>OL</sub>                                                            | —                  | —   | 40                 | mA   |

Table 2.6 lists the nRESET pin specifications for the EM35x. The digital I/O power (named VDD\_PADS) comes from three dedicated pins (pins 23, 28 and 37). The voltage applied to these pins sets the I/O voltage.

| Parameter                        | Test Condition                                                         | Min                | Тур  | Max                | Unit |

|----------------------------------|------------------------------------------------------------------------|--------------------|------|--------------------|------|

| Low Schmitt switching threshold  | V <sub>SWIL</sub><br>Schmitt input threshold going from<br>high to low | 0.42 x<br>VDD_PADS | _    | 0.50 x<br>VDD_PADS | V    |

| High Schmitt switching threshold | V <sub>SWIH</sub><br>Schmitt input threshold going from<br>low to high | 0.62 x<br>VDD_PADS | _    | 0.80 x<br>VDD_PADS | V    |

| Input current for logic 0        | I <sub>IL</sub>                                                        | _                  | —    | -0.5               | μA   |

| Input current for logic 1        | IIH                                                                    | _                  | —    | +0.5               | μA   |

| Input pull-up resistor value     | R <sub>IPU</sub><br>Pull-up value while the chip is not<br>reset       | 24                 | 29   | 34                 | kΩ   |

| Input pull-up resistor value     | R <sub>IPURESET</sub><br>Pull-up value while the chip is<br>reset      | 12                 | 14.5 | 17                 | kΩ   |

## 2.6. Non-RF System Electrical Characteristics

Table 2.7 lists the non-RF system level characteristics for the EM35x.

## Table 2.7. Non-RF System Electrical Characteristics

Measured on Silicon Labs' EM357 reference design with  $T_A$  = 25 °C and  $V_{DD}$  = 3 V, unless otherwise noted.

| Parameter Test Condition            |                                                                                                                                                                                           | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| System wake time from deep<br>sleep | From wakeup event to first ARM <sup>®</sup> Cor-<br>tex <sup>TM</sup> -M3 instruction running from 6 MHz<br>internal RC clock<br>Includes supply ramp time and oscillator<br>startup time |     | 110 |     | μs   |

| Shutdown time going into deep sleep | From last ARM <sup>®</sup> Cortex <sup>TM</sup> -M3 instruction to deep sleep mode                                                                                                        | _   | 5   |     | μs   |

## 2.7. RF Electrical Characteristics

## 2.7.1. Receive

Table 2.8 lists the key parameters of the integrated IEEE 802.15.4-2003 receiver on the EM35x.

Receive measurements were collected with the Silicon Labs EM35x Ceramic Balun Reference Design (Version A0) at 2440 MHz. The typical number indicates one standard deviation above the mean, measured at room temperature ( $25 \,^{\circ}$ C). The min and max numbers were measured over process corners at room temperature.

## Table 2.8. Receive Characteristics

| Parameter                                                 | Test Condition                                                                                      | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|

| Frequency range                                           |                                                                                                     | 2400 |      | 2500 | MHz  |

| Sensitivity (boost mode)                                  | 1% PER, 20 byte packet defined by IEEE 802.15.4-2003;                                               | —    | -102 | -96  | dBm  |

| Sensitivity                                               | 1% PER, 20 byte packet defined by IEEE 802.15.4-2003;                                               | —    | -100 | -94  | dBm  |

| High-side adjacent channel rejection                      | IEEE 802.15.4-2003 interferer signal,<br>wanted IEEE 802.15.4-2003 signal<br>at –82 dBm             | —    | 35   | —    | dB   |

| Low-side adjacent channel rejection                       | IEEE 802.15.4-2003 interferer signal,<br>wanted IEEE 802.15.4-2003 signal<br>at –82 dBm             | —    | 35   | —    | dB   |

| 2 <sup>nd</sup> high-side adjacent channel rejec-<br>tion | IEEE 802.15.4-2003 interferer signal,<br>wanted IEEE 802.15.4-2003 signal<br>at –82 dBm             | —    | 46   | —    | dB   |

| 2 <sup>nd</sup> low-side adjacent channel rejection       | IEEE 802.15.4-2003 interferer signal,<br>wanted IEEE 802.15.4-2003 signal<br>at –82 dBm             |      | 46   | —    | dB   |

| High-side adjacent channel rejection                      | Filtered IEEE 802.15.4-2003 inter-<br>ferer signal, wanted IEEE 802.15.4-<br>2003 signal at –82 dBm | —    | 39   | —    | dB   |

| Low-side adjacent channel rejection                       | Filtered IEEE 802.15.4-2003 inter-<br>ferer signal, wanted IEEE 802.15.4-<br>2003 signal at –82 dBm | —    | 47   | —    | dB   |

| 2 <sup>nd</sup> high-side adjacent channel rejection      | Filtered IEEE 802.15.4-2003 inter-<br>ferer signal, wanted IEEE 802.15.4-<br>2003 signal at –82 dBm | _    | 49   | —    | dB   |

| 2 <sup>nd</sup> low-side adjacent channel rejection       | Filtered IEEE 802.15.4-2003 inter-<br>ferer signal, wanted IEEE 802.15.4-<br>2003 signal at –82 dBm | —    | 49   | —    | dB   |

| High-side adjacent channel rejection                      | CW interferer signal, wanted IEEE<br>802.15.4-2003 signal at –82 dBm                                | —    | 44   | —    | dB   |

| Low-side adjacent channel rejection                       | CW interferer signal, wanted IEEE<br>802.15.4-2003 signal at –82 dBm                                | _    | 47   | —    | dB   |

# Table 2.8. Receive Characteristics (Continued)

| Parameter                                                                                     | Test Condition                                                                          | Min  | Тур | Мах  | Unit |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|-----|------|------|

| 2 <sup>nd</sup> high-side adjacent channel<br>rejection                                       | CW interferer signal, wanted IEEE<br>802.15.4-2003 signal at –82 dBm                    | _    | 59  | —    | dB   |

| 2 <sup>nd</sup> low-side adjacent channel rejection                                           | CW interferer signal, wanted IEEE<br>802.15.4-2003 signal at –82 dBm                    | —    | 59  | —    | dB   |

| Channel rejection for all other channels                                                      | IEEE 802.15.4-2003 interferer signal,<br>wanted IEEE 802.15.4-2003 signal<br>at –82 dBm | —    | 40  | _    | dB   |

| 802.11g rejection centered at +12 MHz<br>or –13 MHz                                           | IEEE 802.15.4-2003 interferer signal,<br>wanted IEEE 802.15.4-2003 signal<br>at –82 dBm | —    | 36  | _    | dB   |

| Maximum input signal level for correct operation                                              |                                                                                         | 0    |     | _    | dBm  |

| Co-channel rejection                                                                          | IEEE 802.15.4-2003 interferer signal,<br>wanted IEEE 802.15.4-2003 signal<br>at –82 dBm | _    | -6  | _    | dBc  |

| Relative frequency error<br>(50% greater than the 2x40 ppm<br>required by IEEE 802.15.4-2003) |                                                                                         | -120 | _   | +120 | ppm  |

| Relative timing error<br>(50% greater than the 2x40 ppm<br>required by IEEE 802.15.4-2003)    |                                                                                         | -120 |     | +120 | ppm  |

| Linear RSSI range                                                                             | As defined by IEEE 802.15.4-2003                                                        | 40   |     |      | dB   |

| RSSI Range                                                                                    |                                                                                         | -90  | _   | -40  | dBm  |

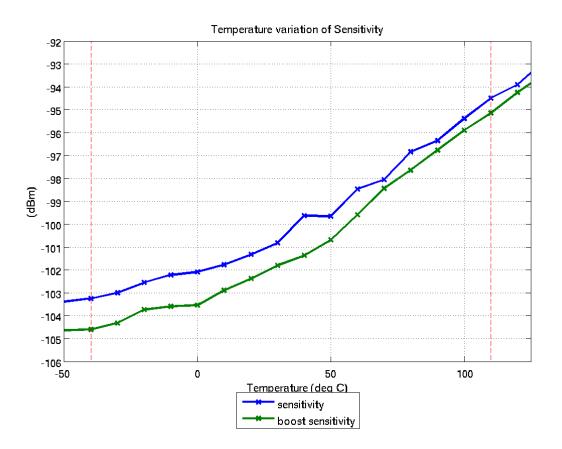

Figure 2.3 shows the variation of receive sensitivity with temperature for boost mode and normal mode for a typical chip.

Figure 2.3. Receive Sensitivity vs. Temperature

## 2.7.2. Transmit

Table 2.9 lists the key parameters of the integrated IEEE 802.15.4-2003 transmitter on the EM35x.

Transmit measurements were collected with the Silicon Labs EM35x Ceramic Balun Reference Design (Version A0) at 2440 MHz. The Typical number indicates one standard deviation below the mean, measured at room temperature (25 °C). The Min and Max numbers were measured over process corners at room temperature. In terms of impedance, this reference design presents a 3n3 inductor in parallel with a 100:50  $\Omega$  balun to the RF pins.

#### Table 2.9. Transmit Characteristics

| Parameter Test Condition               |                                                               | Min | Тур | Max | Unit |

|----------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| Maximum output power<br>(boost mode)   | At highest boost mode power setting (+8)                      | —   | 8   | -   | dBm  |

| Maximum output power                   | At highest normal mode power setting (+3)                     | 1   | 5   | _   | dBm  |

| Minimum output power                   | At lowest power setting                                       |     | -55 | _   | dBm  |

| Error vector magnitude<br>(Offset-EVM) | As defined by IEEE 802.15.4-2003,<br>which sets a 35% maximum | —   | 5   | 15  | %    |

| Carrier frequency error                |                                                               | -40 |     | +40 | ppm  |

| PSD mask relative                      | 3.5 MHz away                                                  | -20 |     |     | dB   |

| PSD mask absolute                      | 3.5 MHz away                                                  | -30 | —   | —   | dBm  |

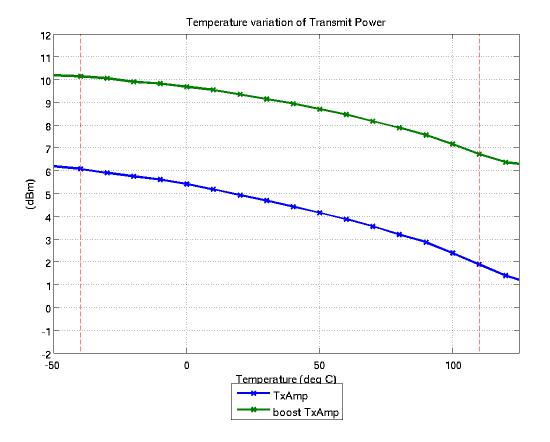

Figure 2.4 shows the variation of transmit power with temperature for maximum boost mode power, and normal mode for a typical chip.

Figure 2.4. Transmit Power vs. Temperature

## 2.7.3. Synthesizer

Table 2.10 lists the key parameters of the integrated synthesizer on the EM35x.

Table 2.10. Synthesizer CharacteristicsMeasured on Silicon Labs' EM357 reference design with  $T_A = 25$  °C and  $V_{DD} = 3$  V, unless otherwise noted.

| Parameter                     | Test Condition                                                                               | Min  | Тур  | Max  | Unit   |

|-------------------------------|----------------------------------------------------------------------------------------------|------|------|------|--------|

| Frequency range               |                                                                                              | 2400 | —    | 2500 | MHz    |

| Frequency resolution          |                                                                                              | —    | 11.7 | —    | kHz    |

| Lock time                     | From off                                                                                     | —    | —    | 100  | μs     |

| Relock time                   | Channel change or RX/TX turnaround<br>(IEEE 802.15.4-2003 defines 192 µs<br>turnaround time) | —    | —    | 100  | μs     |

| Phase noise at 100 kHz offset |                                                                                              | —    | -75  | —    | dBc/Hz |

| Phase noise at 1 MHz offset   |                                                                                              | _    | -100 | _    | dBc/Hz |

| Phase noise at 4 MHz offset   |                                                                                              | _    | -108 | _    | dBc/Hz |

| Phase noise at 10 MHz offset  |                                                                                              | —    | -114 | —    | dBc/Hz |

# 3. Functional Description

The EM351 and EM357 are fully integrated system-on-chips that integrate a 2.4 GHz, IEEE 802.15.4-2003-compliant transceiver, 32-bit ARM<sup>®</sup> Cortex-M3 microprocessor, flash and RAM memory, and peripherals of use to designers of ZigBee-based systems.

The transceiver uses an efficient architecture that exceeds the dynamic range requirements imposed by the IEEE 802.15.4-2003 standard by over 15 dB. The integrated receive channel filtering allows for robust co-existence with other communication standards in the 2.4 GHz spectrum, such as IEEE 802.11-2007 and Bluetooth. The integrated regulator, VCO, loop filter, and power amplifier keep the external component count low. An optional high performance radio mode (boost mode) is software-selectable to boost dynamic range.

The integrated 32-bit ARM<sup>®</sup> Cortex<sup>™</sup>-M3 microprocessor is highly optimized for high performance, low power consumption, and efficient memory utilization. Including an integrated MPU, it supports two different modes of operation—privileged mode and user mode. This architecture could allow for separation of the networking stack from the application code, and prevents unwanted modification of restricted areas of memory and registers resulting in increased stability and reliability of deployed solutions.

The EM351 has 128 kB of embedded flash memory and the EM357 has 192 kB of embedded flash memory. Both chips have 12 kB of integrated RAM for data and program storage. The Ember software for the EM35x employs an effective wear-leveling algorithm that optimizes the lifetime of the embedded flash.

To maintain the strict timing requirements imposed by the ZigBee and IEEE 802.15.4-2003 standards, the EM35x integrates a number of MAC functions, AES128 encryption accelerator, and automatic CRC handling into the hardware. The MAC hardware handles automatic ACK transmission and reception, automatic backoff delay, and clear channel assessment for transmission, as well as automatic filtering of received packets. The Ember Packet Trace Interface is also integrated with the MAC, allowing complete, non-intrusive capture of all packets to and from the EM35x with Ember development tools.

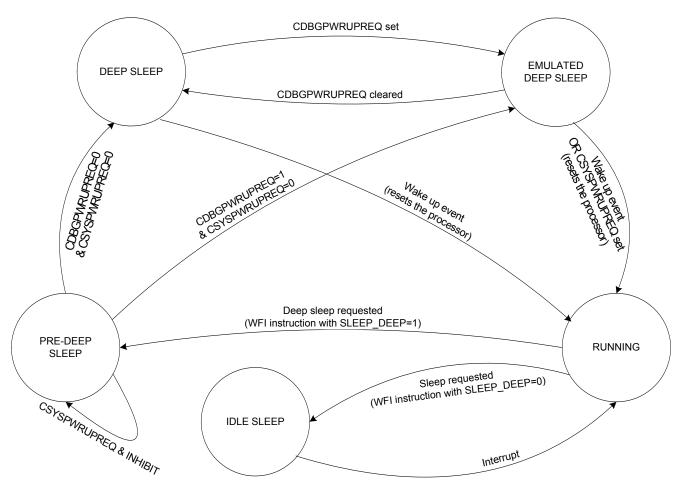

The EM35x offers a number of advanced power management features that enable long battery life. A high-frequency internal RC oscillator allows the processor core to begin code execution quickly upon waking. Various deep sleep modes are available with less than 1  $\mu$ A power consumption while retaining RAM contents. To support user-defined applications, on-chip peripherals include UART, SPI, TWI, ADC, and general-purpose timers, as well as up to 24 GPIOs. Additionally, an integrated voltage regulator, power-on-reset circuit, and sleep timer are available.

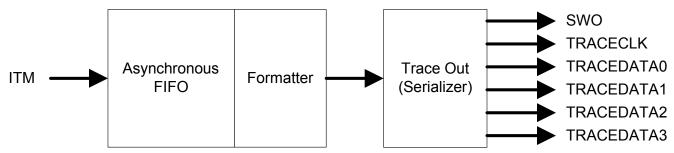

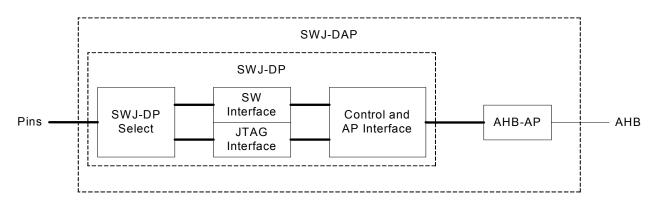

Finally, the EM35x utilizes standard Serial Wire and JTAG interfaces for powerful software debugging and programming of the ARM Cortex<sup>™</sup>-M3 core. The EM35x integrates the standard ARM system debug components: Flash Patch and Breakpoint (FPB), Data Watchpoint and Trace (DWT), and Instrumentation Trace Macrocell (ITM).

Target applications for the EM35x include the following:

- Smart Energy

- Building automation and control

- Home automation and control

- Security and monitoring

- General ZigBee wireless sensor networking

The technical data sheet details the EM35x features available to customers using it with Ember software.

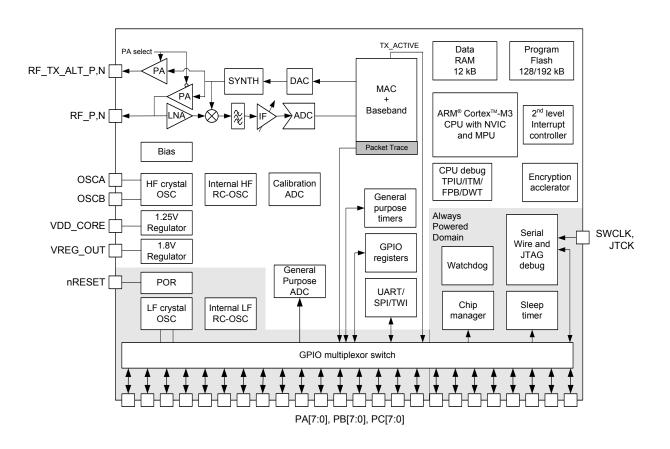

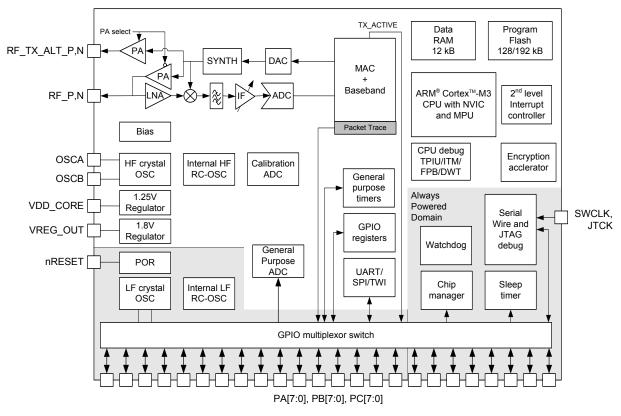

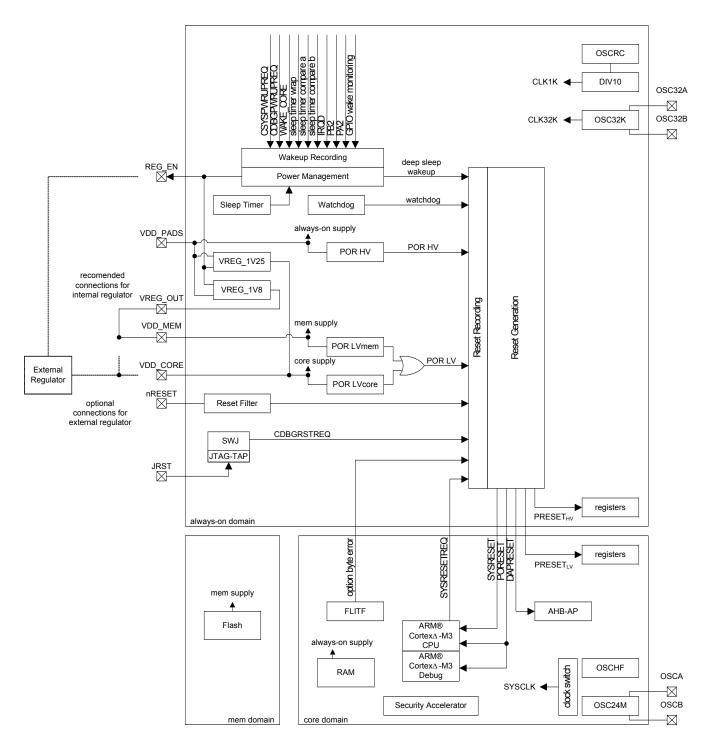

Figure 3.1 shows a detailed block diagram of the EM35x.

Figure 3.1. EM35x Block Diagram

The EM35x radio receiver is a low-IF, super-heterodyne receiver. The architecture has been chosen to optimize coexistence with other devices in the 2.4 GHz band (namely Wi-Fi and Bluetooth), and to minimize power consumption. The receiver uses differential signal paths to reduce sensitivity to noise interference. Following RF amplification, the signal is downconverted by an image-rejecting mixer, filtered, and then digitized by an ADC.

The digital section of the receiver uses a coherent demodulator to generate symbols for the hardware-based MAC. The digital receiver also contains the analog radio calibration routines, and controls the gain within the receiver path.

The radio transmitter uses an efficient architecture in which the data stream directly modulates the VCO frequency. An integrated PA provides the output power. Digital logic controls TX path and output power calibration. If the EM35x is to be used with an external PA, use the TX\_ACTIVE or nTX\_ACTIVE signal to control the timing of the external switching logic.

The integrated 4.8 GHz VCO and loop filter minimize off-chip circuitry. Only a 24 MHz crystal with its loading capacitors is required to establish the PLL local oscillator signal.

The MAC interfaces the on-chip RAM to the RX and TX baseband modules. The MAC provides hardware-based IEEE 802.15.4-2003 packet-level filtering. It supplies an accurate symbol time base that minimizes the synchronization effort of the Ember software and meets the protocol timing requirements. In addition, it provides timer and synchronization assistance for the IEEE 802.15.4-2003 CSMA-CA algorithm.

The EM35x integrates hardware support for a packet trace module, which allows robust packet-based debug. This element is a critical component of Ember Desktop, the Ember development environment, and provides advanced network debug capability when used with the Ember Debug Adapter (ISA3).

The EM35x integrates an ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 microprocessor, revision r1p1. This industry-leading core provides 32-bit performance and is very power-efficient. It has excellent code density using the ARM<sup>®</sup> Thumb-2 instruction set. The processor can be operated at 12 or 24 MHz when using the high-frequency crystal oscillator, or at 6 MHz

or 12 MHz when using the high-frequency internal RC oscillator.

The EM351 has 128 kB of flash memory and the EM357 has 192 kB of flash memory. Both chips have 12 kB of RAM on-chip, and the ARM configurable memory protection unit (MPU).

The EM35x implements both the ARM Serial Wire and JTAG debug interfaces. These interfaces provide real time, non-intrusive programming and debugging capabilities. Serial Wire and JTAG provide the same functionality, but are mutually exclusive. The Serial Wire interface uses two pins; the JTAG interface uses five. Serial Wire is preferred, since it uses fewer pins.

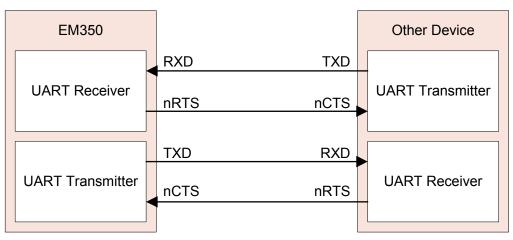

The EM35x contains 24 GPIO pins shared with other peripheral or alternate functions. Because of flexible routing within the EM35x, external devices can use the alternate functions on a variety of different GPIOs. The integrated serial controller SC1 can be configured for SPI (master or slave), TWI (master-only), or UART operation, and the serial controller SC2 can be configured for SPI (master or slave) or TWI (master-only) operation.

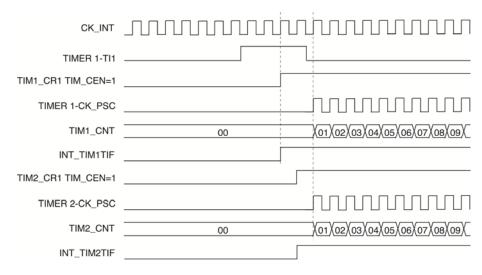

The EM35x has a general purpose ADC which can sample analog signals from six GPIO pins in single-ended or differential modes. It can also sample the 1.8 V regulated supply VDD\_PADSA, the voltage reference VREF, and GND. The ADC has one voltage range: 0 to 1.2 V (normal). The ADC has a DMA mode to capture samples and automatically transfer them into RAM. The integrated voltage reference for the ADC, VREF, can be made available to external circuitry. An external voltage reference can also be driven into the ADC. The regulator input voltage, VDD\_PADS, cannot be measured using the general purpose ADC, but it can be measured through Ember software.

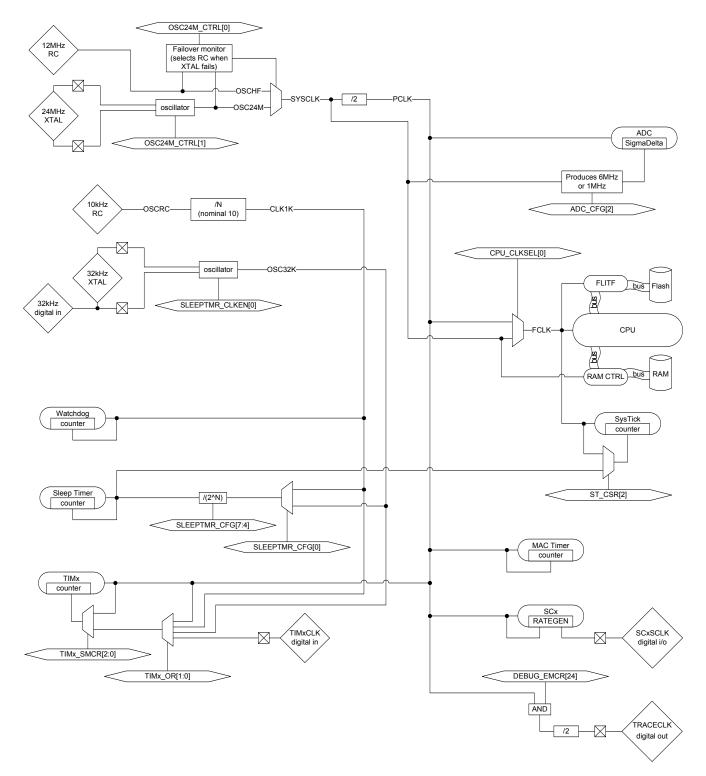

The EM35x contains four oscillators: a high-frequency 24 MHz external crystal oscillator, a high-frequency 12 MHz internal RC oscillator, an optional low-frequency 32.768 kHz external crystal oscillator, and a low-frequency 10 kHz internal RC oscillator.

The EM35x has an ultra low power, deep sleep state with a choice of clocking modes. The sleep timer can be clocked with either the external 32.768 kHz crystal oscillator or with a 1 kHz clock derived from the internal 10 kHz RC oscillator. Alternatively, all clocks can be disabled for the lowest power mode. In the lowest power mode, only external events on GPIO pins will wake up the chip. The EM35x has a fast startup time (typically 110 µs) from deep sleep to the execution of the first ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 instruction.

The EM35x contains three power domains. The always-on high voltage supply powers the GPIO pads and critical chip functions. Regulated low voltage supplies power the rest of the chip. The low voltage supplies are disabled during deep sleep to reduce power consumption. Integrated voltage regulators generate regulated 1.25 V and 1.8 V voltages from an unregulated supply voltage. The 1.8 V regulator output is decoupled and routed externally to supply analog blocks, RAM, and flash memories. The 1.25 V regulator output is decoupled externally and supplies the core logic.

**Note:** The EM35x is not pin-compatible with the previous generation chip, the EM250, except for the RF section of the chip. Pins 1-11 and 45-48 are compatible, to ease migration to the EM35x.

# 4. Radio Module

The radio module consists of an analog front end and digital baseband as shown in Figure 3.1 on page 23.

## 4.1. Receive (RX) Path

The RX path uses a low-IF, super-heterodyne receiver that rejects the image frequency using complex mixing and polyphase filtering. In the analog domain, the input RF signal from the antenna is first amplified and mixed down to a 4 MHz IF frequency. The mixers' output is filtered, combined, and amplified before being sampled by a 12 MSPS ADC. The digitized signal is then demodulated in the digital baseband. The filtering within the RX path improves the EM35x's co-existence with other 2.4 GHz transceivers such as Zigbee/ 802.15.4-2003, IEEE 802.11-2007, and Bluetooth radios. The digital baseband also provides gain control of the RX path, both to enable the reception of small and large wanted signals and to tolerate large interferers.

#### 4.1.1. RX Baseband

The EM35x RX digital baseband implements a coherent demodulator for optimal performance. The baseband demodulates the O-QPSK signal at the chip level and synchronizes with the IEEE 802.15.4-2003-defined preamble. An automatic gain control (AGC) module adjusts the analog gain continuously every ½ symbol until the preamble is detected. Once detected, the gain is fixed for the remainder of the packet. The baseband despreads the demodulated data into 4-bit symbols. These symbols are buffered and passed to the hardware-based MAC module for packet assembly and filtering.

In addition, the RX baseband provides the calibration and control interface to the analog RX modules, including the LNA, RX baseband filter, and modulation modules. The Ember software includes calibration algorithms that use this interface to reduce the effects of silicon process and temperature variation.

#### 4.1.2. RSSI and CCA

The EM35x calculates the RSSI over every 8-symbol period as well as at the end of a received packet. The linear range of RSSI is specified to be at least 40 dB over temperature. At room temperature, the linear range is approximately 60 dB (–90 dBm to –30 dBm input signal).

The EM35x RX baseband provides support for the IEEE 802.15.4-2003 RSSI CCA method. Clear channel reports busy medium if RSSI exceeds its threshold.

## 4.2. Transmit (TX) Path

The EM35x TX path produces an O-QPSK-modulated signal using the analog front end and digital baseband. The area- and power-efficient TX architecture uses a two-point modulation scheme to modulate the RF signal generated by the synthesizer. The modulated RF signal is fed to the integrated PA and then out of the EM35x.

#### 4.2.1. TX Baseband

The EM35x TX baseband in the digital domain spreads the 4-bit symbol into its IEEE 802.15.4-2003-defined 32chip sequence. It also provides the interface for the Ember software to calibrate the TX module to reduce silicon process, temperature, and voltage variations.

#### 4.2.2. TX\_ACTIVE and nTX\_ACTIVE Signals

For applications requiring an external PA, two signals are provided called TX\_ACTIVE and nTX\_ACTIVE. These signals are the inverse of each other. They can be used for external PA power management and RF switching logic. In transmit mode the TX baseband drives TX\_ACTIVE high, as described in Table 7.5 on page 57. In receive mode the TX\_ACTIVE signal is low. TX\_ACTIVE is the alternate function of PC5, and nTX\_ACTIVE is the alternate function of PC6. See "7. GPIO (General Purpose Input/Output)" on page 50 for details of the alternate GPIO functions. The digital I/O that provide these signals have a 4 mA output sink and source capability.

## 4.3. Calibration

The Ember software calibrates the radio using dedicated hardware resources.

## 4.4. Integrated MAC Module

The EM35x integrates most of the IEEE 802.15.4-2003 MAC requirements in hardware. This allows the ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 CPU to provide greater bandwidth to application and network operations. In addition, the hardware acts as a first-line filter for unwanted packets. The EM35x MAC uses a DMA interface to RAM to further reduce the overall ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 CPU interaction when transmitting or receiving packets.

When a packet is ready for transmission, the Ember software configures the TX MAC DMA by indicating the packet buffer RAM location. The MAC waits for the backoff period, then switches the baseband to TX mode and performs channel assessment. When the channel is clear the MAC reads data from the RAM buffer, calculates the CRC, and provides 4-bit symbols to the baseband. When the final byte has been read and sent to the baseband, the CRC remainder is read and transmitted.

The MAC is in RX mode most of the time. In RX mode various format and address filters keep unwanted packets from using excessive RAM buffers, and prevent the CPU from being unnecessarily interrupted. When the reception of a packet begins, the MAC reads 4-bit symbols from the baseband and calculates the CRC. It then assembles the received data for storage in a RAM buffer. RX MAC DMA provides direct access to RAM. Once the packet has been received additional data, which provides statistical information on the packet to the Ember software, is appended to the end of the packet in the RAM buffer space.

The primary features of the MAC are as follows:

- CRC generation, appending, and checking

- Hardware timers and interrupts to achieve the MAC symbol timing

- Automatic preamble and SFD pre-pending on TX packets

- Address recognition and packet filtering on RX packets

- Automatic acknowledgment transmission

- Automatic transmission of packets from memory

- Automatic transmission after backoff time if channel is clear (CCA)

- Automatic acknowledgment checking

- Time stamping received and transmitted messages

- Attaching packet information to received packets (LQI, RSSI, gain, time stamp, and packet status)

- IEEE 802.15.4-2003 timing and slotted/unslotted timing

## 4.5. Packet Trace Interface (PTI)

The EM35x integrates a true PHY-level PTI for effective network-level debugging. It monitors all the PHY TX and RX packets between the MAC and baseband modules without affecting their normal operation. It cannot be used to inject packets into the PHY/MAC interface. This 500 kbps asynchronous interface comprises the frame signal (PTI\_EN, PA4) and the data signal (PTI\_DATA, PA5). PTI is supported by the Ember development tools.

## 4.6. Random Number Generator

Thermal noise in the analog circuitry is digitized to provide entropy for a true random number generator (TRNG). The TRNG produces 16-bit uniformly distributed numbers. The Ember software uses the TRNG to seed a pseudo random number generator (PRNG). The TRNG is also used directly for cryptographic key generation.

# 5. ARM<sup>®</sup> Cortex<sup>™</sup>-M3 and Memory Modules

This chapter discusses the ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 Microprocessor, and reviews the EM35x's flash and RAM memory modules as well as the Memory Protection Unit (MPU).

# 5.1. ARM<sup>®</sup> Cortex<sup>™</sup>-M3 Microprocessor

The EM35x integrates the ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 microprocessor, revision r1p1, developed by ARM Ltd., making the EM35x a true System-on-Chip solution. The ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 is an advanced 32-bit modified Harvard architecture processor that has separate internal program and data buses, but presents a unified program and data address space to software. The word width is 32 bits for both the program and data sides. The ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 allows unaligned word and half-word data accesses to support efficiently-packed data structures.

The ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 clock speed is configurable to 6 , 12 , or 24 MHz. For normal operation 24 MHz is preferred over 12 MHz due to improved performance for all applications and improved duty cycling for applications using sleep modes. The 6 MHz operation can only be used when radio operations are not required since the radio requires an accurate 12 MHz clock.

The ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 in the EM35x has also been enhanced to support two separate memory protection levels. Basic protection is available without using the MPU, but normal operation uses the MPU. The MPU allows for protecting unimplemented areas of the memory map to prevent common software bugs from interfering with software operation. The architecture could also allow for separation of the networking stack from the application code using a fine granularity RAM protection module. Errant writes are captured and details are reported to the developer to assist in tracking down and fixing issues.

## 5.2. Embedded Memory

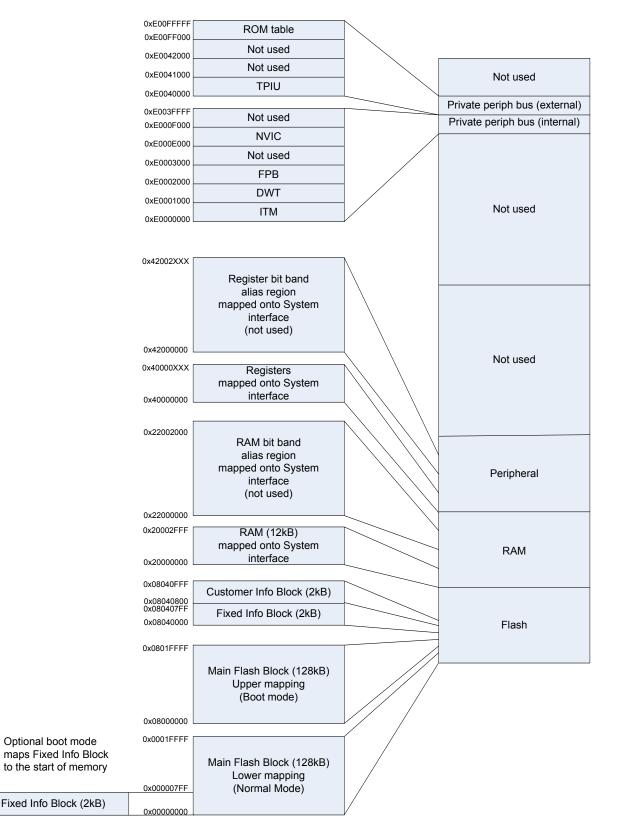

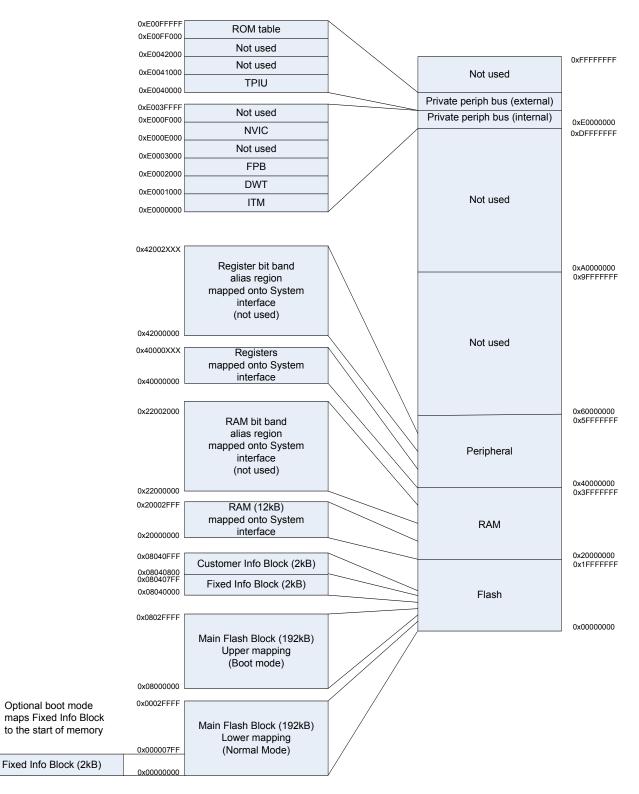

Figure 5.1 shows the EM351 ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 memory map and Figure 5.2 shows the EM357 ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 memory map.

Figure 5.1. EM351 ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 Memory Map

Figure 5.2. EM357 ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 Memory Map

#### 5.2.1. Flash Memory

#### 5.2.1.1. Flash Overview

The EM351 provides a total of 132 kB of flash memory and the EM357 provides a total of 196 kB of flash memory. The flash memory is provided in three separate blocks:

- Main Flash Block (MFB)

- Fixed Information Block (FIB)

- Customer Information Block (CIB)

The MFB is divided into 2048-byte pages. The EM351 has 64 pages and the EM357 has 96 pages. The CIB is a single 2048-byte page. The FIB is a single 2048-byte page. The smallest erasable unit is one page and the smallest writable unit is an aligned 16-bit half-word. The flash is rated to have a guaranteed 20,000 write/erase cycles. The flash cell has been qualified for a data retention time of >100 years at room temperature.

Flash may be programmed either through the Serial Wire/JTAG interface or through bootloader software. Programming flash through Serial Wire/JTAG requires the assistance of RAM-based utility code. Programming through a bootloader requires Ember software for over-the-air loading or serial link loading.

#### 5.2.1.2. Main Flash Block

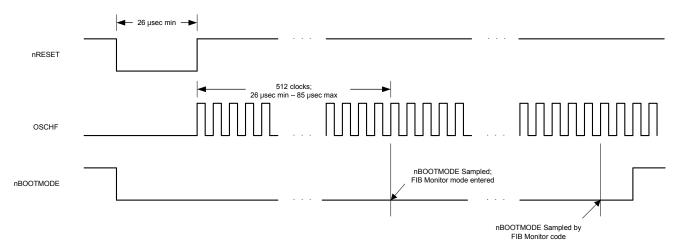

The start of the MFB is mapped to both address 0x00000000 and address 0x08000000 in normal boot mode, but is mapped only to address 0x08000000 in FIB monitor mode (see also "7.5. Boot Configuration" on page 53). Consequently, it is recommended that software intended to execute from the MFB is designed to operate from the upper address, 0x08000000, since this address mapping is always available in all modes.

The MFB stores all program instructions and constant data. A small portion of the MFB is devoted to non-volatile token storage using the Ember Simulated EEPROM system.

#### 5.2.1.3. Fixed Information Block

The 2 kB FIB is used to store fixed manufacturing data including serial numbers and calibration values. The start of the FIB is mapped to address 0x08040000. This block can only be programmed during production by Silicon Labs.

The FIB also contains a monitor program, which is a serial-link-only way of performing low-level memory accesses. In FIB monitor mode (see "7.5. Boot Configuration" on page 53), the start of the FIB is mapped to both address 0x00000000 and address 0x08040000 so the monitor may be executed out of reset.

#### 5.2.1.4. Customer Information Block

The 2048 byte CIB can be used to store customer data. The start of the CIB is mapped to address 0x08040800. The CIB cannot be executed.

The first eight half-words of the CIB are dedicated to special storage called option bytes. An option byte is a 16 bit quantity of flash where the lower 8 bits contain the data and the upper 8 contain the inverse of the lower 8 bits. The upper 8 bits are automatically generated by hardware and cannot be written to by the user, see Table 5.1.

The option byte hardware also verifies the inverse of each option byte when exiting from reset and generates an error, which prevents the CPU from executing code, if a discrepancy is found. All of this is transparent to the user.

| Address    | bits [15:8]           | bits [7:0]    | Notes                                          |

|------------|-----------------------|---------------|------------------------------------------------|

| 0x08040800 | Inverse Option Byte 0 | Option Byte 0 | Configures flash read protection               |

| 0x08040802 | Inverse Option Byte 1 | Option Byte 1 | Reserved                                       |

| 0x08040804 | Inverse Option Byte 2 | Option Byte 2 | Available for customer use <sup>1</sup>        |

| 0x08040806 | Inverse Option Byte 3 | Option Byte 3 | Available for customer use <sup>1</sup>        |

| 0x08040808 | Inverse Option Byte 4 | Option Byte 4 | Configures flash write protection              |

| 0x0804080A | Inverse Option Byte 5 | Option byte 5 | Configures flash write protection              |

| 0x0804080C | Inverse Option Byte 6 | Option Byte 6 | Configures flash write protection <sup>2</sup> |

| 0x0804080E | Inverse Option Byte 7 | Option Byte 7 | Reserved                                       |

| Notes:     |                       |               |                                                |

## Table 5.1. Option Byte Storage

1. Option bytes 2 and 3 do not link to any specific hardware functionality other than the option byte loader.

Therefore, they are best used for storing data that requires a hardware verification of the data integrity.

2. Option byte 6 is reserved/unused in the EM351 due to the smaller flash size.

Table 5.2 shows the mapping of the option bytes that are used for read and write protection of the flash. Each bit of the flash write protection option bytes protects a 4 page region of the main flash block. The EM351 has 16 regions and therefore option bytes 4 and 5 control flash write protection (option byte 6 is reserved/unused). The EM357 has 24 regions and therefore option bytes 4, 5, and 6 control flash write protection. These write protection bits are active low, and therefore the erased state of 0xFF disables write protection. Like read protection, write protection only takes effect after a reset. Write protection not only prevents a write to the region, but also prevents page erasure.

Option byte 0 controls flash read protection. When option byte 0 is set to 0xA5, read protection is disabled. All other values, including the erased state 0xFF, enable read protection when coming out of reset. The internal state of read protection (active versus disabled) can only be changed by applying a full chip reset. If a debugger is connected to the EM35x, the intrusion state is latched. Read protection is combined with this latched intrusion signal. When both read protection and intrusion are set, all flash is disconnected from the internal bus. As a side effect, the CPU cannot execute code since all flash is disconnected from the bus. This functionality prevents a debug tool from being able to read the contents of any flash. The only means of clearing the intrusion signal is to disconnect the debugger and reset the entire chip using the nRESET pin. By requiring a chip reset, a debugger cannot install or execute malicious code that could allow the contents of the flash to be read.

The only way to disable read protection is to program option byte 0 with the value 0xA5. Option byte 0 must be erased before it can be programmed. Erasing option byte 0 while read protection is active automatically masserases the main flash block. By automatically erasing main flash, a debugger cannot disable read protection and readout the contents of main flash without destroying its contents.

When read protection is active, the bottom four flash pages, addresses 0x08000000 to 0x08001FFF, are automatically write-protected. Write protecting the bottom four flash pages of main flash prevents an attacker from reprogramming the reset vector and executing arbitrary code.

In general, if read protection is active then write protection should also be active. This prevents an attacker from reprogramming flash with malicious code that could readout the flash after the debugger is disconnected. Even though read protection automatically protects the reset vector, the same technique of reprogramming flash could be performed at an address outside the bottom four flash pages. To obtain fully protected flash, both read protection and write protection should be active.

| Option Byte                | Bit            | Notes                                                     |  |  |  |

|----------------------------|----------------|-----------------------------------------------------------|--|--|--|

| Option Byte 0              | bit [7:0]      | Read protection of all flash (MFB, FIB, CIB)              |  |  |  |

| Option Byte 1              | bit [7:0]      | Reserved for Silicon Labs use                             |  |  |  |

| Option Byte 2              | bit [7:0]      | Available for customer use                                |  |  |  |

| Option Byte 3              | bit [7:0]      | vailable for customer use                                 |  |  |  |

| Option Byte 4              | bit [0]        | Write protection of address range 0x08000000 – 0x08001FFF |  |  |  |

|                            | bit [1]        | Write protection of address range 0x08002000 – 0x08003FFF |  |  |  |

|                            | bit [2]        | Write protection of address range 0x08004000 – 0x08005FFF |  |  |  |

|                            | bit [3]        | Write protection of address range 0x08006000 – 0x08007FFF |  |  |  |

|                            | bit [4]        | Write protection of address range 0x08008000 – 0x08009FFF |  |  |  |

|                            | bit [5]        | Write protection of address range 0x0800A000 – 0x0800BFFF |  |  |  |

|                            | bit [6]        | Write protection of address range 0x0800C000 – 0x0800DFFF |  |  |  |

|                            | bit [7]        | Write protection of address range 0x0800E000 – 0x0800FFFF |  |  |  |

| Option Byte 5              | bit [0]        | Write protection of address range 0x08010000 – 0x08011FFF |  |  |  |

|                            | bit [1]        | Write protection of address range 0x08012000 – 0x08013FFF |  |  |  |

|                            | bit [2]        | Write protection of address range 0x08014000 – 0x08015FFF |  |  |  |

|                            | bit [3]        | Write protection of address range 0x08016000 – 0x08017FFF |  |  |  |

|                            | bit [4]        | Write protection of address range 0x08018000 – 0x08019FFF |  |  |  |

|                            | bit [5]        | Write protection of address range 0x0801A000 – 0x0801BFFF |  |  |  |

|                            | bit [6]        | Write protection of address range 0x0801C000 – 0x0801DFFF |  |  |  |

|                            | bit [7]        | Write protection of address range 0x0801E000 – 0x0801FFFF |  |  |  |

| Option Byte 6 <sup>*</sup> | bit [0]        | Write protection of address range 0x08020000 – 0x08021FFF |  |  |  |

|                            | bit [1]        | Write protection of address range 0x08022000 – 0x08023FFF |  |  |  |

|                            | bit [2]        | Write protection of address range 0x08024000 – 0x08025FFF |  |  |  |

|                            | bit [3]        | Write protection of address range 0x08026000 – 0x08027FFF |  |  |  |

|                            | bit [4]        | Write protection of address range 0x08028000 – 0x08029FFF |  |  |  |

|                            | bit [5]        | Write protection of address range 0x0802A000 – 0x0802BFFF |  |  |  |

|                            | bit [6]        | Write protection of address range 0x0802C000 – 0x0802DFFF |  |  |  |

|                            | bit [7]        | Write protection of address range 0x0802E000 – 0x0802FFFF |  |  |  |

| Option Byte 7              | bit [7:0]      | Reserved for Silicon Labs use                             |  |  |  |

| *Note: Option byt          | e 6 is reserve | ed/unused in the EM351 due to the smaller flash size.     |  |  |  |

Table 5.2. Option Byte Write Protection Bit Map

#### 5.2.1.5. Simulated EEPROM

Ember software reserves 8 kB of the main flash block as a simulated EEPROM storage area for stack and customer tokens. The simulated EEPROM storage area implements a wear-leveling algorithm to extend the number of simulated EEPROM write cycles beyond the physical limit of 20,000 write cycles for which each flash cell is gualified.

#### 5.2.2. RAM

#### 5.2.2.1. RAM Overview